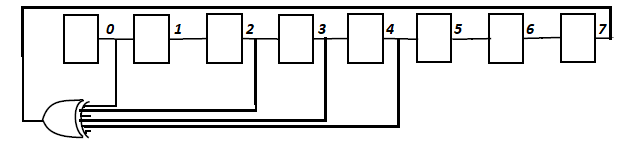

I made some slight modifications to what you had (you are pretty much there though) I don’t think the LFSR would step properly otherwise.The majority of logic designers use the first two types, because they’re simple to implement in Verilog or VHDL. This page contains VHDL tutorial, VHDL Syntax, VHDL Quick Reference, modelling memory and FSM, Writing Testbenches in VHDL, Lot of VHDL Examples. Most of the EE or CS graduates know or at least have heard about different types of hardware counters: prescaled, Johnson, ripple carry, linear feedback shift register (LFSR), and others.These Linear-feedback shift register (LFSR) is a shift applications require low power dissipation for VLSI register whose input bit is a linear function of its circuits. Government and industry organizations are valuable partners at Duke ECE, and our entrepreneurial spirit manifests itself in a growing portfolio of companies. Dukes Electrical and Computer Engineering research enables creative, applicable solutions to pressing challenges in human health, security, and automation, and new strides in fundamental scientific exploration and discovery.

Vhdl Lfsr Code From This

Language Templates-VHDL-Synthesis Constructs-Coding Examples- Counters-LFSR. I pick up LFSR code from this path on ISE. I write below Vhdl code & testbench code for implement LFSR on ISE. First using an LFSR approach and secondly using a lookup table for speed.1. Is a command-line application that generates Verilog or VHDL code for CRC.

Vhdl Lfsr Series Of Numbers

With careful construction, the The other day I run into Xilinx LFSR Counter core and decided to explore its advantages. This results in the shift register producing a pseudo-random series of numbers. An LFSR is essentially a shift register where a few of the bits are set to result of XOR-ing other bits in the register. Can you Help me,PleaseBuild a 4-bit linear-feedback shift register (LFSR).

Chain 3+ LFSR’s and you can get different ‘pairs’ of consecutive numbers, depending on which counter is currently active. This would then pause the currently used counter and start the next one (or reconfigure the taps to get same effect). Xilinx Linear Feedback Shift Register (LFSR) Logic a few thoughts here:A) You can make something like a NAND gate (think of how address decoders work) setup where only a certain pattern of 1’s and 0’s will trigger it. Maria George and Peter Alfke, Linear Feedback Shift Registers in Virtex Devices, Xilinx application note Xapp210 Peter Alfke, Efficient Shift Registers, LFSR Counters, and Long Pseudo-Random Sequence Generators,

This method does not suffer from any change in timing (in theory!) since the gates take roughly the same time rather a given input is 0 or 1.The goal being to still be pretty basic logic, that runs with low latency, while providing less trivial sequences. This would be used to change the behavior so that there’s effectively hidden states, that reconfigure say, a NAND to an AND, or an XOR to an X-NOR, or invert single inputs of NAND gates (same as how NOR/NAND/OR/AND can be equivalent with inverted inputs and outputs). This idea leads to part C… hidden states.C) You can make a counter with a second set of states (besides the ‘taps’ or output number in other words). If counter A has a period of 2, and counter B has a period of 3, then there’s 6 unique possible states.

0 kommentar(er)

0 kommentar(er)